Du befindest dich hier: FSI Informatik » Prüfungsfragen und Altklausuren » Prüfungen im Bachelor-Studium (1. - 5. Semester) » gra » Aufgabe 1: Allgemein

Inhaltsverzeichnis

Aufgabe 1: Allgemein

1. Speicher

wahr | falsch (nicht alle) | wahr | falsch (nicht bit sondern Byte)

2. Assemblerprogrammierung

wahr | flasch(Flag register bedingt) | wahr | wahr | falsch(.date auch möglich) | falsch

3. Speicherschutz

falsch(mischform möglich) | wahr | wahr | falsch (mmu nur paging) | falsch | falsch (gilt nur für phy.A.) | wahr | falsch

Aufgabe 2: Mikroprogrammierung

1)

Pseudocode:

if(eingabe < 0) goto SPEICHER ZEROCHECK: if(eingabe-1 < 0) goto ENDE SPEICHER: speicher = eingabe

MicroCode:

START: eingabe -> D D-> B | D -> E B->C if(C>=0) goto ZEROCHECK SPEICHER: E-> Speicher goto START ZEROCHECK: B-1 -> C if(C>=0) goto SPEICHER ENDE:

2)

Bei der Festverdrahteten sind die Befehle alle gleich groß und können daher in einem Takt decodiert werden. Bei der Mikroprogrammierung dauert das länger und es muss auch erst das Mikroprogramm geladen werden.

3)

Da Macro auf Micro abgebildet wird. Bei Macro gibt es ja die Sprünge.

Aufgabe 3: Speicherverwaltung

1)

–TODO–

2)

Page fault. da das pressend bit nicht gesetzt ist

3)

Virtuelle Adresse | Physikalische Adresse | Flags

Valid-Bit wird nicht gespeichert, denn alle Bits müssen valid sein.

4)

Bei Segmentierung, denn da wird die Adresse berechnet (Segmentsanfangsadresse + Offset) wobei bei Paging nur zusammengesetzt wird aus Basis & Offset.

5)

2^N * 1 Byte

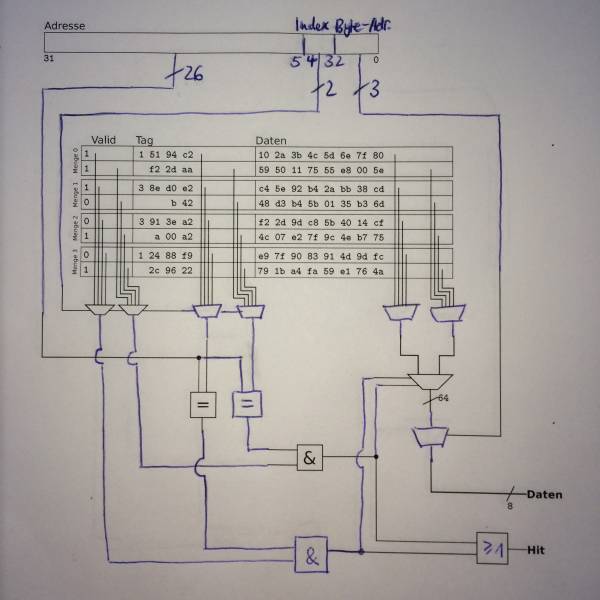

Aufgabe 4: Cache

1)

hort ist schneller, weil dadurch die vertikal liegenden Blöcke, welche im Cache stehen, besser genutzt werden können bevor ein Cache Miss auftritt.

2)

Da Befehle und Daten sich nicht gegenseitig verdrängen. Befehle und Daten werden bei räumlicher und zeitlicher Lokalität anders gemappt.

3)

Dann müsste man 2 Speicherblöcke auslesen um 1 Datum zu erhalten, was Zeit kostet.

4)

#blocke = s / b #menge = (#blocke / n) f(addr_i) = (addr_i / b) % #menge

5)

Vollassoziativ, denn es gibt für jeden Cache-Eintrag einen Vergleicher und es gibt keinen Index.

6)

Aufgabe 5: Umformung

1)

Code umformen und auf ALU-Operation achten.

int test (int x , int n){

int akku = 0;

int ret = 0;

int i = 0;

akku = i;

goto LCOND

LOOP:

int diff2 = 0;

akku = wert[i];

akku = akku - x;

akku = akku * akku;

diff2 = akku;

if(akku > 100){

ret = 1;

goto END

}

akku = i;

akku = akku + 1;

i = akku;

LCOND:

if(akku < n) goto LOOP

END:

Aufgabe 6: Assembler

1)

* Sprungmarken(Labels)

Sprungadresse

* Funktionsaufrufe mit Parametern

call

* Globale Variablen

Liegen im .daten Segment

* Lokale Variablen (auf dem Stack)

Stack reservierung Push Pop

* Kommentare

Keine

2)

ebp: er zeigt auf denn den befehl nach dem call befehl und weis damit auf den Letzten Stack Frame wo das Programm wieder zurück springt

3)

Memory-Mapped-I/O: Damit kann mann ganz normal auf die IO Geräte mit z.b. Mov zugreifen

Isolated-I/O: Mann kann nur mit Speziellen Load befehlen auf die IO zugreifen

4)

RISC: Code Dichte geringer, da Festverdrahtet.

CISC: Code Dichte ist wegen der Mikroprogrammierung höher.

5)

Bei rekursive Algorithmen: Da es dort sehr viele Rücksprungadressen gibt.

Aufgabe 7: Prozessorarchitekturen

1)

Speedup = T1/ Tk = (n*s*t) / (s+(n-1))*t = n*s / s+(n-1) = lim n→inf n*s/s+(n-1) = s

Speedup = s

2)

VLIW muss die Hardware für den Compiler bekannt sein und damit die anzahl der ALUS damit die programme laufen können Superskalar wird komplet vom Prozessor gehändelt und die programme müssen nicht speziel für geschrieben werden(compiler).

3)

Zeitscheiben MT: Jeder Prozess hat immer genau gleich viel zeit zu arbeiten keiner verhungert

Erreignis gesteuerte MT: Wenn der prozessor auf etwas warten muss bis etwas fertig ist dann kann er so lange einen anderen Prozess abarbeiten.

Simultanes MT: es werden Prozesse ausgewahlt die gerade ausgeführt werden (was abgearbeitet werden kann wird abgearbeitet)

4)

Er muss Threads Erstellen

5)

| index | BHBD | OH | AS | RS |

|---|---|---|---|---|

| 0 | movl(1) | - | - | - |

| 1 | movl(2) | movl(1) | - | - |

| 2 | movl(3) | movl(2) | mov(1) | - |

| 3 | addl(4) | movl(3) | movl(2) | movl(1) |

| 4 | addl(4) | - | movl(3) | movl(2) |

| 5 | addl(4) | - | - | movl(3) |

| 6 | addl(5) | add(4) | - | |

| 7 | addl(5) | - | add(4) | - |

| 8 | addl(5) | - | - | add(4) |

| 9 | - | add(5) | - | - |

| 10 | - | - | add(5) | - |

| 11 | - | - | - | add(5) |

| 12 | - | - | - | - |

Speed up daher

4(Stufen) * 5(befehle) / 12 (ausführungschritte)

6)

da das programm auf abhängigkeiten warten muss

FORUM

Falls ihr Fehler findet, oder Fragen habt ist hier der Thread im Forum dazu zum Forum