# Universität Erlangen-Nürnberg Technische Fakultät Lehrstuhl für Hardware-Software-Co-Design Prof. Dr.-Ing. Jürgen Teich

# Klausur Technische Informatik 1

13. September 2006

| Name            |  |

|-----------------|--|

| Matrikelnummer  |  |

| Studienrichtung |  |

| Aufgabe          | 1  | 2  | 3  | 4  | 5  | Σ  |

|------------------|----|----|----|----|----|----|

| max. Punkte      | 20 | 20 | 10 | 20 | 20 | 90 |

| erreichte Punkte |    |    |    |    |    |    |

| Note             |    |    |    |    |    |    |

### Aufgabe 1 (Zahlendarstellung)

(20 Punkte)

Zum Erreichen der vollen Punktzahl muss der Lösungsweg erkennbar sein.

- a) Konvertieren Sie die Zahl  $43,4343_{(6)}$  in eine Zahl zur Basis  $4(x_{(4)})$  unter ausschließlicher Verwendung der gegebenen Zahlensysteme. (5 Punkte)

- b) Berechnen Sie  $42_{(7)}-42_{(10)}$  im Binärsystem, und geben Sie das Ergebnis im Zweier-komplement als 10-Bit Zahl an. (4 Punkte)

- c) Subtrahieren Sie die folgenden 16-Bit Gleitkommazahlen unter Beibehaltung der Gleitkommadarstellung:

x1 = 0100010000110100 (Minuend)

$x^2 = 1011110110011001$  (Subtrahent)

Die Bestandteile der Gleitkommazahlen sind von links: Vorzeichen (1 Bit), Exponent (7 Bit) und Mantisse (8 Bit). Der Bias beträgt 63. (7 Punkte)

Bei Flash-Speichern werden die Informationen in Kapazitäten von Transistoren gespeichert. In der Vergangenheit konnte pro Transistor immer nur ein Bit gespeichert werden. So entspricht beispielsweise eine '1' einer vollständig geladenen Kapazität und eine '0' entsprechend einer Jeeren Kapazität. Bei einigen aktuellen Flashspeichern können pro Transistor mehr als nur zwei Ladungspegel sicher unterschieden werden.

- d) Wieviele Transistoren sind in einem Flashspeicher zur Speicherung eines Bytes minimal erforderlich, wenn vier Ladungspegel pro Transistor unterschieden werden können?

(1 Punkt)

- e) Ab welcher Anzahl von Bits ist es erstmalig möglich, einen Speichertransistor einzusparen, wenn sechs statt vier Ladungspegel pro Transistor unterschieden werden können? (3 Punkte)

# Aufgabe 2 (Logikminimierung)

(20 Punkte)

In dieser Aufgabe soll ein Schaltnetz entworfen werden, welches den vier Bit breiten binär Codierten Eingang (a,b,c,d) in einen Stibitz-Code umsetzt. Ein Stibitz-Code ergibt sich, wenn auf jede Ziffer einer BCD-Zahl eine binäre  $0011_{(2)}$  addiert wird. Wird an dem Eingang des Schaltnetzes der Wert einer Pseudotetrade angelegt, so liefert der Ausgang den Wert des Eingangs.

|   | U              | ,     | , |   |   |                       |                       |            |                                         |                                                                                                     |

|---|----------------|-------|---|---|---|-----------------------|-----------------------|------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------|

|   | Hex            | Binär |   |   |   | Stibitz               |                       |            |                                         |                                                                                                     |

|   |                | а     | b | С | d | <i>y</i> <sub>3</sub> | <i>y</i> <sub>2</sub> | <i>y</i> 1 | <i>y</i> <sub>0</sub>                   | BCD                                                                                                 |

|   | 0              | 0     | 0 | 0 | 0 |                       |                       |            | *************************************** | БСБ                                                                                                 |

|   | 1              | 0     | 0 | 0 | 1 |                       |                       |            |                                         |                                                                                                     |

|   | 2              | 0     | 0 | 1 | 0 | 1                     |                       |            |                                         |                                                                                                     |

|   | 3              | 0     | 0 | 1 | 1 |                       |                       |            |                                         |                                                                                                     |

| • | 4              | 0     | 1 | 0 | 0 |                       |                       |            |                                         | $v_0 = f_0(a, b)$                                                                                   |

|   | 5              | 0     | 1 | 0 | 1 |                       |                       |            |                                         | $\begin{bmatrix} 1 & 1 & 1 & y_0 = f_0(a, b, a) \\ a & b & c & d \end{bmatrix}  y_0 = f_1(a, b, a)$ |

|   | 6              | 0     | 1 | 1 | 0 |                       |                       |            |                                         | $y_1 = f_1(a, b, c)$                                                                                |

|   | 7              | 0     | 1 | 1 | 1 |                       |                       |            |                                         | a b c d $y_1 = f_1(a, b, a)$<br>?? $y_2 = f_2(a, b, a)$                                             |

| • | 8              | 1     | 0 | 0 | 0 |                       |                       |            |                                         | $y_3  y_2  y_1  y_0 \qquad y_3 = f_3(a,b,a)$                                                        |

|   | 9              | 1     | 0 | 0 | 1 |                       |                       |            |                                         |                                                                                                     |

|   | A              | 1     | 0 | 1 | 0 |                       |                       |            |                                         |                                                                                                     |

|   | В              | 1     | 0 | 1 | 1 |                       |                       |            |                                         | ·                                                                                                   |

| • | $\overline{C}$ | 1     | 1 | 0 | 0 |                       |                       |            |                                         | . 7                                                                                                 |

|   | D              | 1     | 1 | 0 | 1 |                       |                       |            |                                         | <b>V</b>                                                                                            |

|   | F F            | 1     | 1 | 1 | 0 |                       |                       |            |                                         | Stibitz                                                                                             |

|   | F              | 1     | 1 | 1 | 1 |                       |                       |            |                                         | SHUILZ                                                                                              |

|   | F              | 1     | 1 | 1 | 1 |                       |                       |            |                                         |                                                                                                     |

a) Vervollständigen Sie in der Tabelle den Stibitz-Code.

(2 Punkte)

b) Geben Sie die Konjunktive Normalform (KNF) für das Signal  $y_1$  an.

(1 Punkt)

c) Ermitteln Sie die Disjunktiven Minimalformen (DMF) für die Steuersignale  $y_0$  und  $y_3$  mit Hilfe von Symmetriediagrammen.

(4 Punkte)

- d) Bestimmen Sie eine kostengünstige minimale disjunktive Ansteuerungsfuntion für das Signal  $y_2$  mit Hilfe der Verfahren von Quine-McCluskey und von Petrick. (Die Kosten ergeben sich aus der Anzahl von Literalen pro Term.) (7 Punkte)

- e) Das Schaltnetz für das Signal  $y_3$  soll durch Verwendung von NAND-Gattern mit zwei Eingängen realisiert werden. Ermitteln Sie den entsprechenden Schaltalgebraischen Ausdruck für das Signal  $y_3$  aus Teilaufgabe c) und zeichnen Sie das entsprechende Schaltnetz. (4 Punkte)

- f) Welche Alternative zu der hier verwendeten Behandlung der Pseudotetraden bietet sich auch noch an? Welche Vorteile bietet diese Alternative? (2 Punkte)

### Aufgabe 3 (Fehlerkorrektur)

(10 Punkte)

- a) Wieviele Prüfbits sind bei einer Blocksicherung zur Korrektur von Einzelbitfehlern minimal erforderlich, wenn ein Block aus je 32 Informationsbits bestehen soll? (1 Punkt)

- b) In wieviele Zeilen sind die Informationsbits zu packen, damit die minimale Anzahl von Prüfbits aus Aufgabe a) genutzt werden kann?

Geben Sie alle Möglichkeiten an.

- c) Sind für den Fall a) bei der Verwendung eines Hamming-Codes weniger Prüfbits erforderlich? Begründen Sie Ihre Aussage.

(2 Punkte)

- d) Wieviele Prüfstellen sind bei Verwendung eines Hamming-Codes erforderlich, wenn Einzelbitfehler in Codierungen mit 16 Informationsstellen korrigierbar sein soll? (1 Punkt)

- e) Geben Sie für den Fall d) die Booleschen Ausdrücke für die Berechnung aller Prüfstellen an. (3 Punkte)

# Aufgabe 4 (VHDL)

(20 Punkte)

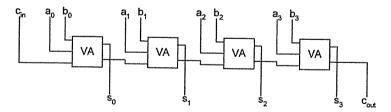

Das Ziel dieser Aufgabe ist es, eine VHDL-Beschreibung eines n-Bit Carry-Ripple-Addierers (siehe Abbildung) zu entwickeln und anschließend durch eine Testbench zu verifizieren.

- a) Geben Sie eine Schnittstellenbeschreibung eines Halbaddierers in Form einer Entity in VHDL an! (2 Punkte)

- b) Geben Sie eine Implementierung eines Halbaddierers in Form einer VHDL-Architecture an! (2 Punkte)

- c) Geben Sie eine Implementierung eines Volladdierers in Form einer VHDL-Architecture an! Der Volladdierer nutzt dabei Instanzen des zuvor entwickelten Halbaddierers.

(2 Punkte)

d) Geben Sie nun eine Implementierung eines generischen n-Bit Ripple-Carry-Addierers in Form einer VHDL-Architecture an. Benutzen Sie dabei die in den vorherigen Teilaufgaben entwickelten Module! (6 Punkte)

Hinweis: Dabei bietet es sich an, an geeigneter Stelle das in VHDL vorgesehene generate-Statement zu benutzen.

Bitte Rückseite beachten!

e) Schreiben Sie eine VHDL-Testbench für einen 4-Bit Ripple-Carry-Addierer. Die Testbench soll alle möglichen Eingangsbelegungen nacheinander im Abstand von jeweils 100ns anlegen und im Falle eines Fehlers eine Textausgabe erzeugen. (8 Punkte)

### Aufgabe 5 (Schaltwerke)

(20 Punkte)

Entwerfen Sie ein synchrones Schaltwerk für einen Süßigkeitenautomaten. Der Automat erlaubt nur den Einwurf von 5 und 10 Cent Münzen. Alle übrigen Münzen sollen in dieser Aufgabe nicht betrachtet werden. Ferner gibt es keine Wechselgeldausgabe und zuviel gezahltes Geld wird nicht zurückgegeben! Es stehen zwei Arten von Süßigkeiten zur Auswahl: Kaugummis zu 10 Cent und Lollis zu 15 Cent. Mittels zweier Auswahlknöpfe, einer für Kaugummi und einer für Lolli, wählt man zuerst das gewünschte Produkt aus. Ein gleichzeitiges Drücken der Auswahlknöpfe wird ignoriert. Anschließend wirft man den entsprechenden Betrag ein.

Der Automat besitzt auch einen Geldrückgabeknopf, welcher eingeworfenes Geld wieder zurück gibt, bevor der korrekte Betrag eingeworfen wurde. Denn sobald der komplette Betrag eingeworfen wurde, wird im nächsten Taktzyklus das gewählte Produkt ausgegeben und der Automat kehrt in seinen Grundzustand zurück. Das Drücken eines der drei Taster wird dem Schaltwerk durch eine '1' für die Dauer einer Taktperiode signalisiert. Die Ausgänge Lolli, Kaugummi und Geld\_zurueck sollen ebenfalls für einen Taktzyklus aktiv sein.

- a) Um welchen Automatentypen handelt es sich? Bitte begründen! (1 Punkt)

- b) Geben Sie einen Automatengraphen für den beschriebenen Automaten an. (6 Punkte)

- c) Wieviele Zustandsbits sind zur Codierung der Zustände notwendig?

Geben Sie eine Codierung der Zustände an. (1 Punkt)

- d) Codieren Sie die Ein- und Ausgabe.

(2 Punkte)

e) Geben Sie eine zu b) passende Automatentafel mit codierten Ein- und Ausgaben sowie Zuständen an. (2 Punkte)

Betrachten Sie für die weiteren Teilaufgaben die folgende Tabelle, welche unabhängig von dem obigen Süßigkeitenautomaten ist. Gegeben sind die Codierungen des aktuellen Zustands  $Q^n$ , die Codierungen des Eingangs X, sowie die Codierungen der Folgezustände  $Q^{n+1}$  und des Ausgangs Y.

|   | Q       | ) <sup>n</sup> | 2 | ζ | $Q^n$       | 1+1         | FF2   | FF1   | Y |

|---|---------|----------------|---|---|-------------|-------------|-------|-------|---|

| • | $q_2^n$ | $q_1^n$        | b | а | $q_2^{n+1}$ | $q_1^{n+1}$ | $T_2$ | $T_1$ | у |

| • | 0       | 0              | 0 | 0 | 0           | 0           |       |       | 0 |

|   | 0       | 0              | 0 | 1 | 0           | 1           |       |       | 0 |

|   | 0       | 0              | 1 | 0 | 1           | 1           |       |       | 0 |

|   | 0       | 0              | 1 | 1 | 1           | 0           |       |       | 0 |

| • | 0       | 1              | _ | 0 | 1           | 0           |       |       | 0 |

|   | 0       | 1              | _ | 1 | 0           | 1           |       |       | 0 |

|   | 1       | 0              |   | 0 | 1           | 0           |       |       | 1 |

|   | 1       | 0              | 0 | 1 | 1           | 1           |       |       | 1 |

|   | 1       | 0              | 1 | 1 | 1           | 0           |       |       | 1 |

|   | 1       | 1              | 0 |   | 1           | 1           |       |       | 1 |

|   | 1       | 1              | 1 |   | 0           | 0           |       |       | 1 |

- f) Bestimmen Sie die Ansteuerfunktionen für eine Realisierung des Automaten mit T-Flipflops. (1 Punkt)

- g) Bestimmen Sie anhand der Tabelle den Automatentyp.

(1 Punkt)

- h) Übertragen Sie die Ansteuerfunktionen T1 und T2 in zwei Symmetriediagramme und bestimmen Sie die Disjunktive Minimalform (DMF). (2 Punkte)

- i) Realisieren Sie die Ansteuerfunktionen mittels eines PAL-Bausteines und zeichnen Sie den vollständigen Automaten. (4 Punkte)